Panmnesia Showcases PCIe 6.4 / CXL 3.2 Fabric Switch and Pilot System at CES 2026

Share

Daejeon, South Korea — January 2026 — Panmnesia, a company providing link solution for AI infrastructure, announced that it is exhibiting its PCIe 6.4 and CXL 3.2–compliant fabric switch chip, PANSWITCH™ (model H1SW06245ACFAA), along with PANRDK™, a development board designed for pilot system deployment and validation, at CES 2026, taking place January 6–9 in Las Vegas.

PANSWITCH™ is the world’s first fabric switch that fully supports the key features defined in the CXL 3.2 specification, including Port-based Routing (PBR). Designed for large-scale computing environments such as AI data centers and high-performance computing (HPC) systems, the switch delivers high flexibility and performance. The company is currently in the process of providing switch silicon samples and pilot systems to early access partners.

Panmnesia PCIe 6.4 / CXL 3.2 Fabric Switch

Large-scale AI applications such as ChatGPT are rapidly becoming pervasive across everyday life. These applications rely on the close collaboration of numerous accelerators and memory devices, making inter-device communication overhead a critical determinant of overall system performance.

To address this challenge, Panmnesia developed PANSWITCH™ with a set of differentiated features optimized specifically for large-scale AI workloads.

Traditionally, large-scale device interconnection has relied on network-based approaches such as Ethernet. However, these approaches inherently incur long latencies due to overhead of software stack related to network. Instead of relying on the conventional network, PANSWITCH™ enables a large number of devices to interconnect directly via CXL. Through switch cascading, thousands of devices can be connected using CXL, significantly reducing communication overhead by eliminating network-related software latency. In addition, Panmnesia highlights topology flexibility as a key differentiator of PANSWITCH™.

Communication patterns vary widely depending on the AI application, and optimal performance requires tailoring the system topology to match these patterns. PANSWITCH™ satisfy this demands by supporting not only Hierarchy-based Routing (HBR) but also Port-based Routing (PBR) as defined in the CXL 3.2 specification. This enables users to freely configure a wide range of topologies—from simple tree structures to mesh, dragonfly, and 3D torus—optimizing data movement paths for specific workloads.

Furthermore, PANSWITCH™ integrates Panmnesia’s proprietary ultra-low-latency CXL controller, further minimizing communication latency between devices.

Through the combination of ▲network overhead elimination, ▲support for diverse topologies, and ▲an integration of ultra-low-latency controller, PANSWITCH™ delivers enhanced communication performance and efficiency, enabling acceleration of large-scale AI workloads.

PANRDK™: A Link Development Board for Pilot System Deployment

Panmnesia also unveiled PANRDK™, a link development board designed for pilot system construction, which enables partners to test and validate the switch in real-world environments, PANRDK™ is a board designed by Panmnesia, equipped with an FPGA and supports the high speed of PCIe Gen6. Depending on the IPs loaded onto the FPGA, each board can operate as a variety of CXL devices, including CXL CPUs, CXL GPUs, and CXL memory devices.

Using onboard MCIO and CEM slots, PANRDK™ can be connected to Panmnesia’s switch chips as well as other devices and boards to construct a complete CXL-enabled system. The board is compatible not only with Panmnesia devices but also with a wide range of third-party devices that comply with the CXL standard. Within these systems configured with PANRDK™, users can evaluate practical functionality and system performance, from fundamental read/write operations through full-scale AI and HPC workloads.

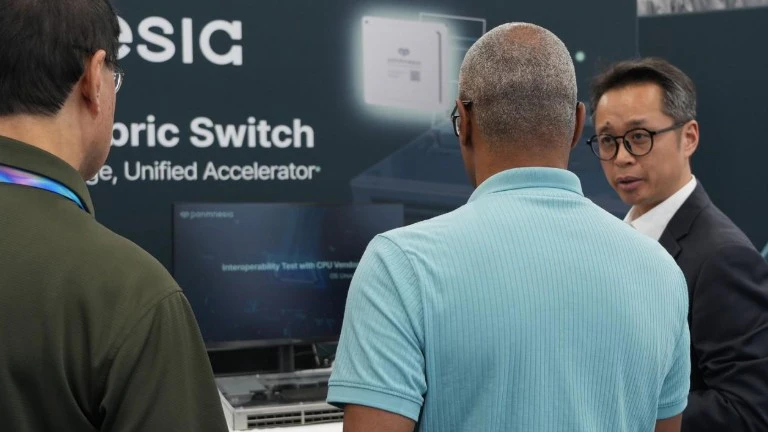

CES 2026 Exhibition

Panmnesia is exhibiting PANSWITCH™ and PANRDK™ at CES 2026, held January 6–9, 2026, in Las Vegas. A Panmnesia representative commented, “Companies developing or operating AI infrastructure solutions showed strong interest in our switch samples and pilot systems during the exhibition,” adding, “We will continue to advance real-world validation and ecosystem development through our expanding partnerships.”

Availability

Panmnesia’s PCIe 6.4/CXL 3.2 Fabric Switch Silicon is out now and early access partners can request samples and pilot systems. For more information about samples, products, and partnership, please contact [email protected].