Panmnesia Showcases High Fan-Out CXL 3.x Switch Solution at CXL DevCon 2025

Share

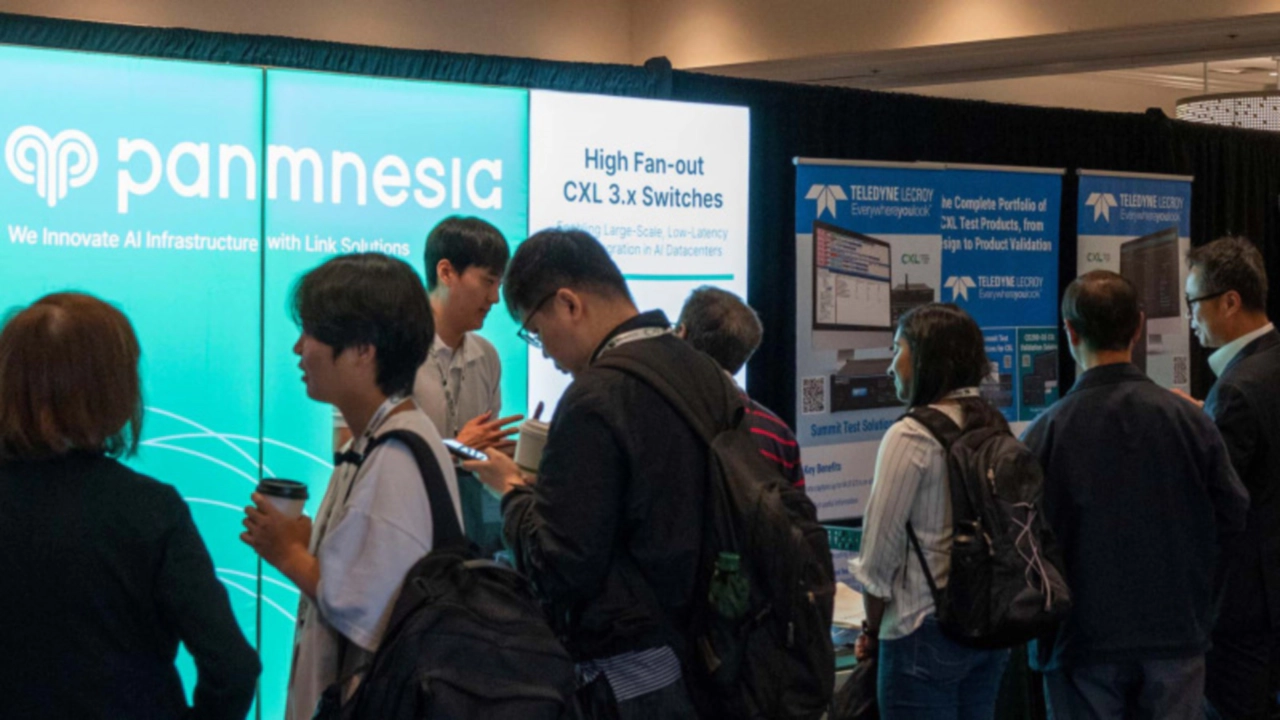

Santa Clara, CA — April 30, 2025 — Panmnesia, a startup specializing in advanced link solutions for AI infrastructure, participated as an exhibitor at this year’s CXL DevCon, hosted by the Compute Express Link (CXL) Consortium. At the event held in Santa Clara, California, Panmnesia showcased its high fan-out CXL 3.x Switch–based framework designed for next-generation AI infrastructure and high-performance computing (HPC) systems.

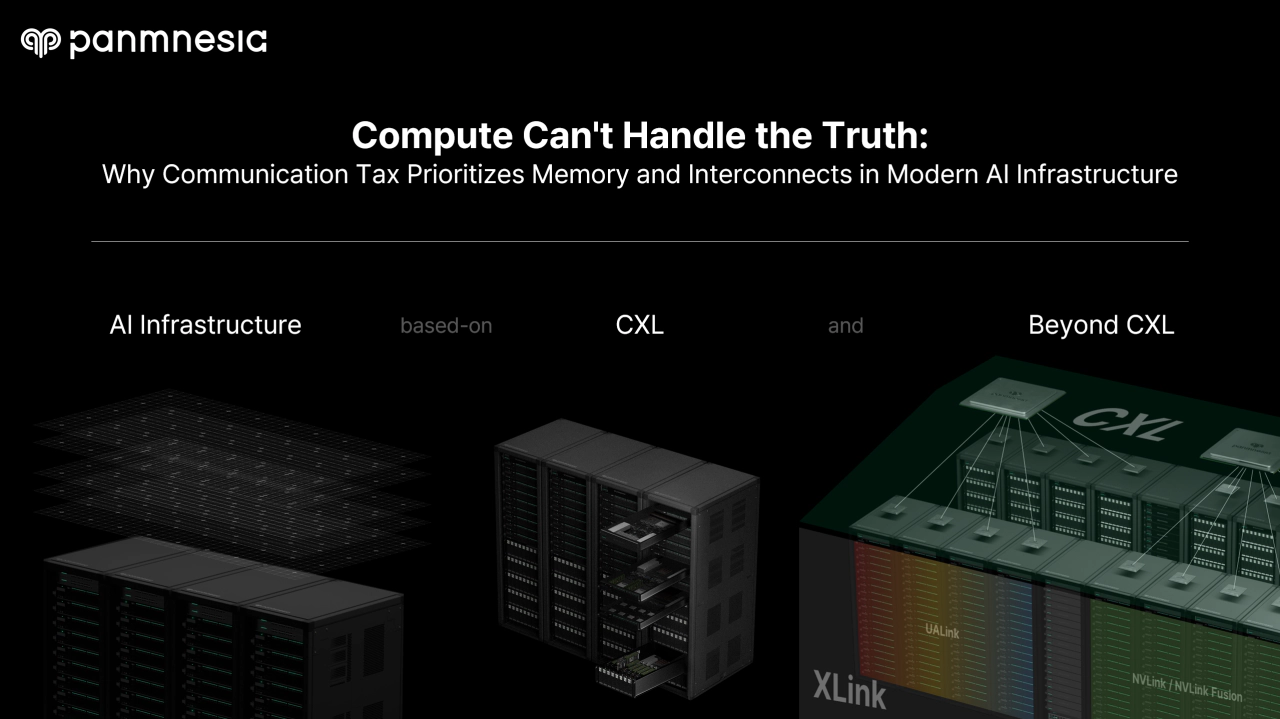

CXL: A Key Enabler for the Efficient Construction of Next-Generation Data Centers As large-scale AI services become increasingly widespread, the importance of building computing infrastructure capable of operating these services efficiently is coming to the forefront. In this context, Compute Express Link (CXL), a high-speed interconnect technology, is gaining significant attention as a core enabler for next-generation computing infrastructure.

CXL is attracting attention primarily for two key reasons: (1) reducing infrastructure deployment costs and (2) minimizing performance overhead. First, CXL enables pooling, which allows different types of system devices to be grouped and managed separately. When a particular type of device is insufficient, only the relevant resource pool—such as a memory pool or GPU pool—can be selectively expanded, thereby minimizing unnecessary resource waste and reducing infrastructure costs. Additionally, CXL-based systems guarantee cache coherency in a hardware-automated manner, which helps minimize overhead from memory management operations and redundant data copying, ultimately improving overall system efficiency.

CXL DevCon 2025: Official Event by the CXL Consortium Amidst these technological trends, CXL DevCon 2025 was held as the official event organized by the CXL Consortium, offering a comprehensive view of the current state and future direction of the CXL ecosystem. The event featured product showcases from consortium members and invited talks from experts leading CXL standardization.

After gaining attention at CXL DevCon 2024 for demonstrating interoperability of its CXL intellectual property (IP), Panmnesia returned this year as an exhibitor, presenting a framework built based on its high fan-out CXL 3.x Switches.

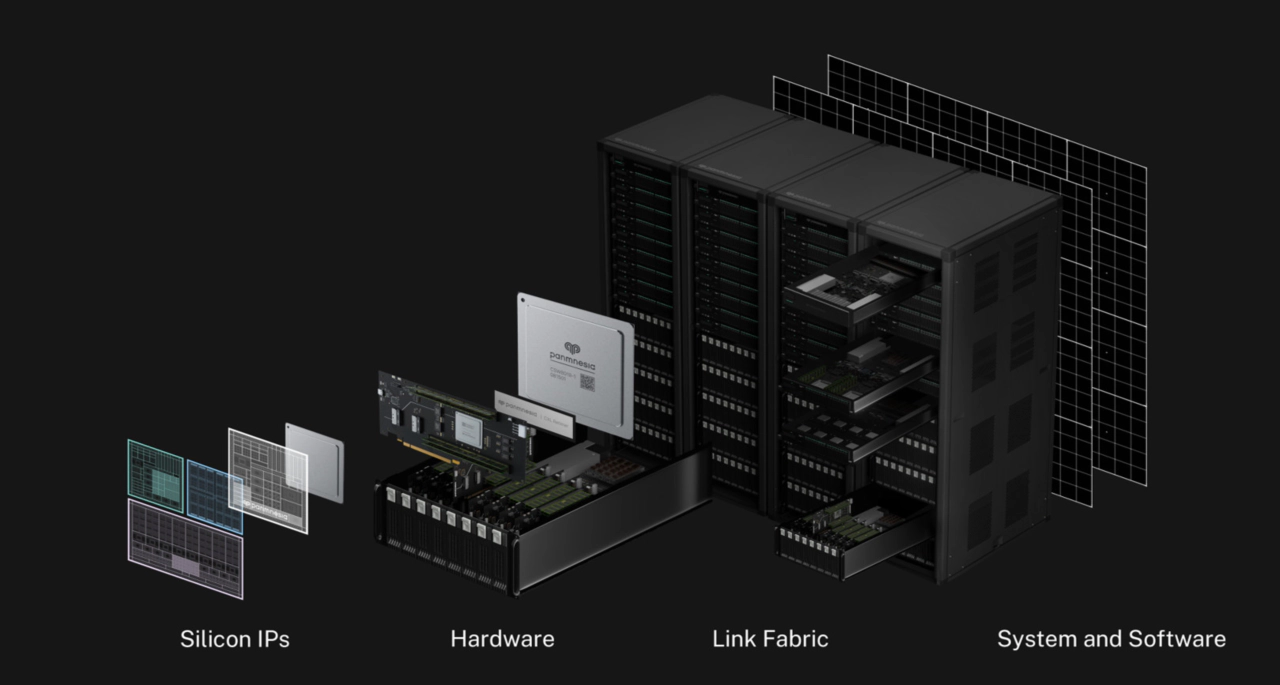

Panmnesia's Exhibit: High Fan-Out CXL 3.x Switch–Based Framework

Panmnesia’s CXL 3.x Switch SoC acts as a backbone interconnect, unifying diverse CXL devices into a cache-coherent system.

• Low Latency Developed based on Panmnesia’s proprietary low-latency CXL IP, the Switch SoC further reduces system latency by minimizing the average number of hops through its high fan-out structure, which allows more devices to be connected simultaneously.

• Scalable & Flexible Architecture The switch supports multi-level switching, allowing multiple switches to be connected across hierarchical layers, as well as port-based routing (PBR), which enables flexible system topology—including both the physical connection structure and data routing paths—based on device port IDs. It also supports connections to all types of system devices—including CPUs, GPUs, and memory modules—making it ideal for constructing large-scale systems in various configurations to meet specific application needs.

At the exhibition, Panmnesia showcased a CXL 3.x Composable Server consisting of multiple CXL-enabled server nodes interconnected via Panmnesia’s CXL 3.x Switch. Each node featured disaggregated CPU, GPU, and memory resources powered by Panmnesia’s CXL IP. This composable architecture enables dynamic system configuration based on workload demands, helping to reduce infrastructure costs. Using this framework, Panmnesia demonstrated how CXL can accelerate AI and HPC workloads—including retrieval-augmented generation (RAG), large language models (LLMs), and scientific simulations—attracting strong interest from other CXL technology companies.

Panmnesia’s Technical Presentation At the event, Dr. Yongjin Cho, Executive Vice President of Panmnesia, delivered a technical presentation highlighting the capabilities of Panmnesia’s CXL 3.x Switches. He introduced example solutions enabled by the technology and shared real-world use cases of CXL 3.x Switch–based infrastructure. Dr. Cho also participated in in-depth discussions with other CXL Consortium members regarding ecosystem development. As the only company to deliver a session addressing CXL 3.x Switch technologies, Panmnesia drew interest from specialists exploring next-generation architectural solutions.

“In CXL DevCon 2025, we received numerous inquiries from attendees—many of whom were exploring CXL 3.x Switch deployments for the first time,” said a company representative. “We look forward to expanding collaboration with partners to help advance the CXL 3.x ecosystem,” the representative added.

This content has also been featured in the following article.