Two-Digit Nanosecond CXL 3.2 Link Controller IP

Link Controller IP implements critical logics allowing your hardware to communicate over the CXL network. Our optimized architecture offers two-digit nanosecond roundtrip latency, providing significant performance gain in demanding workloads such as AI, HPC, and cloud.

Key Benefits

Silicon -Proven CXL 3.2 Compliance

Ensure one-shot silicon success for your design and reduce time-to-market. Link Controller IP also offers full CXL 3.2 feature support rigorously tested in multiple scenarios.

Configurable to Fit Your Need

Easily achieve your design goals. Link Controller IP offers diverse set of options you can configure for your memory expander, accelerator, and CPU design.

Best-In-Class Power Consumption

Save the power budget for your hardware design. Our precision architecture ensures the lowest power consumption for the controller IP.

Key Features

Our product in more details

Specification | CXL 3.2 Backward compatible with CXL 1.1, 2.0, and PCIe Gen 6 |

Number of Lanes | Up to 16 |

Data Rate | 64 GT/s |

Roundtrip Latency | < 100ns |

Bifurcation Support | x1, x2, x4, x8, x16 |

Supported Sub-Protocols | CXL.io, CXL.mem, CXL.cache Unordered IO support Back-invalidation support Direct P2P support |

Supported Device Types | CXL type 1/2/3 device support Multi-Logical Device (MLD) support Multi-Headed Device (MHD) support Fabric-Attached Memory (FAM) support |

Flit Format | 68B, 256B, 256B standard, 256B LOpt support |

Optimization Features | Multi-Data Header (MDH) support Address Translation Service (ATS) support ARB/MUX bypass support Arbitration and data multiplexing/demultiplexing support |

Latency Management | Sync header bypass support Drift buffer support |

Power Management | Low-power mode support |

Security Features | Integrity and Data Encryption (IDE) feature support Advanced Error Reporting (AER) support |

All specifications are subject to change without notice. Performance may vary based on system configuration and usage patterns.

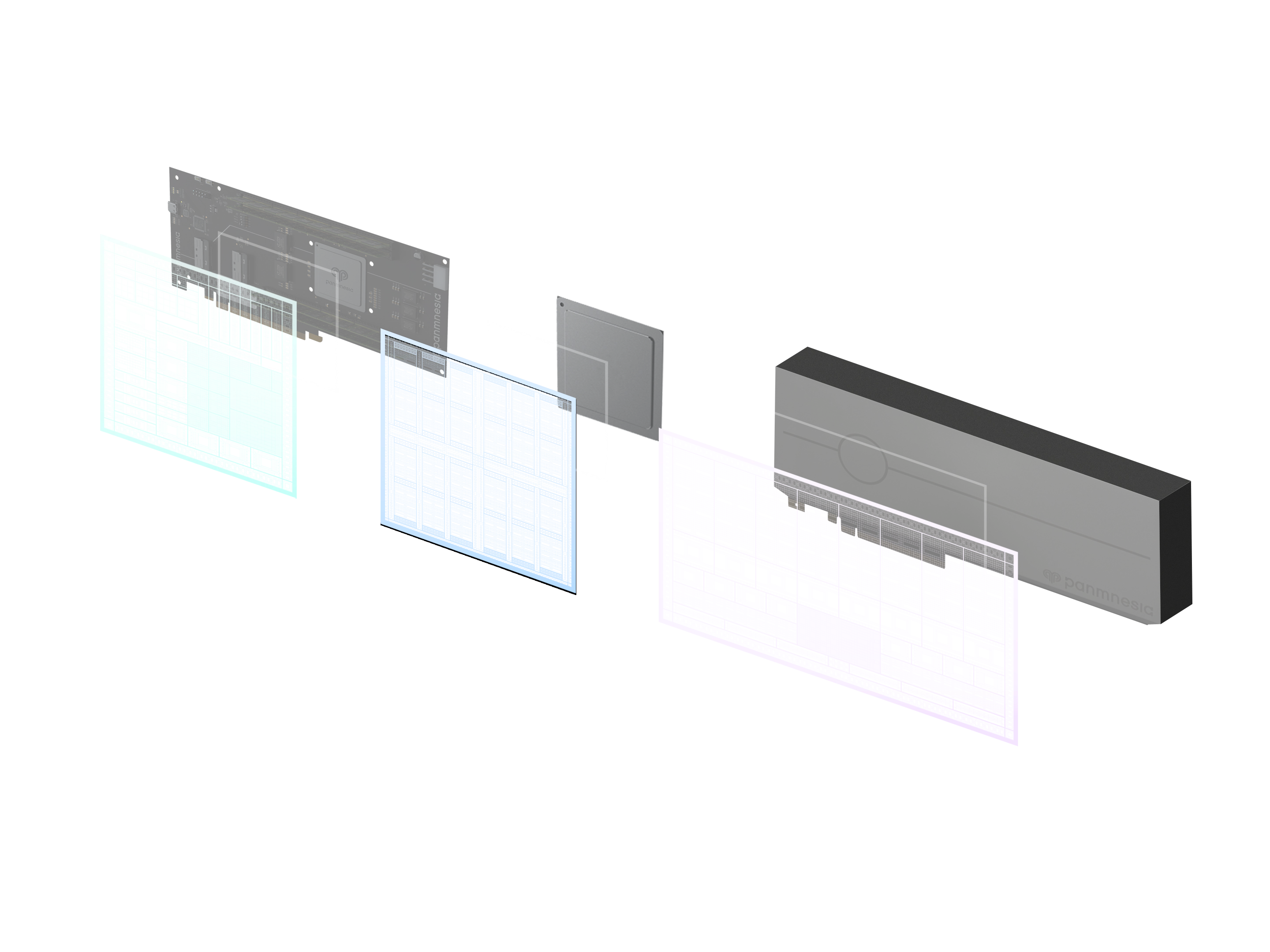

IP Architecture

CXL 3.2 Link Controller IP is composed of CXL controller and a PCIe controller, which handles CXL.cache/mem and CXL.io respectively. The IP allows configuration and status report through a set of registers. The IP can be connected to a user logic directly, or through the Link Acceleration Unit IP for faster time-to-market.

Real-world Use Cases

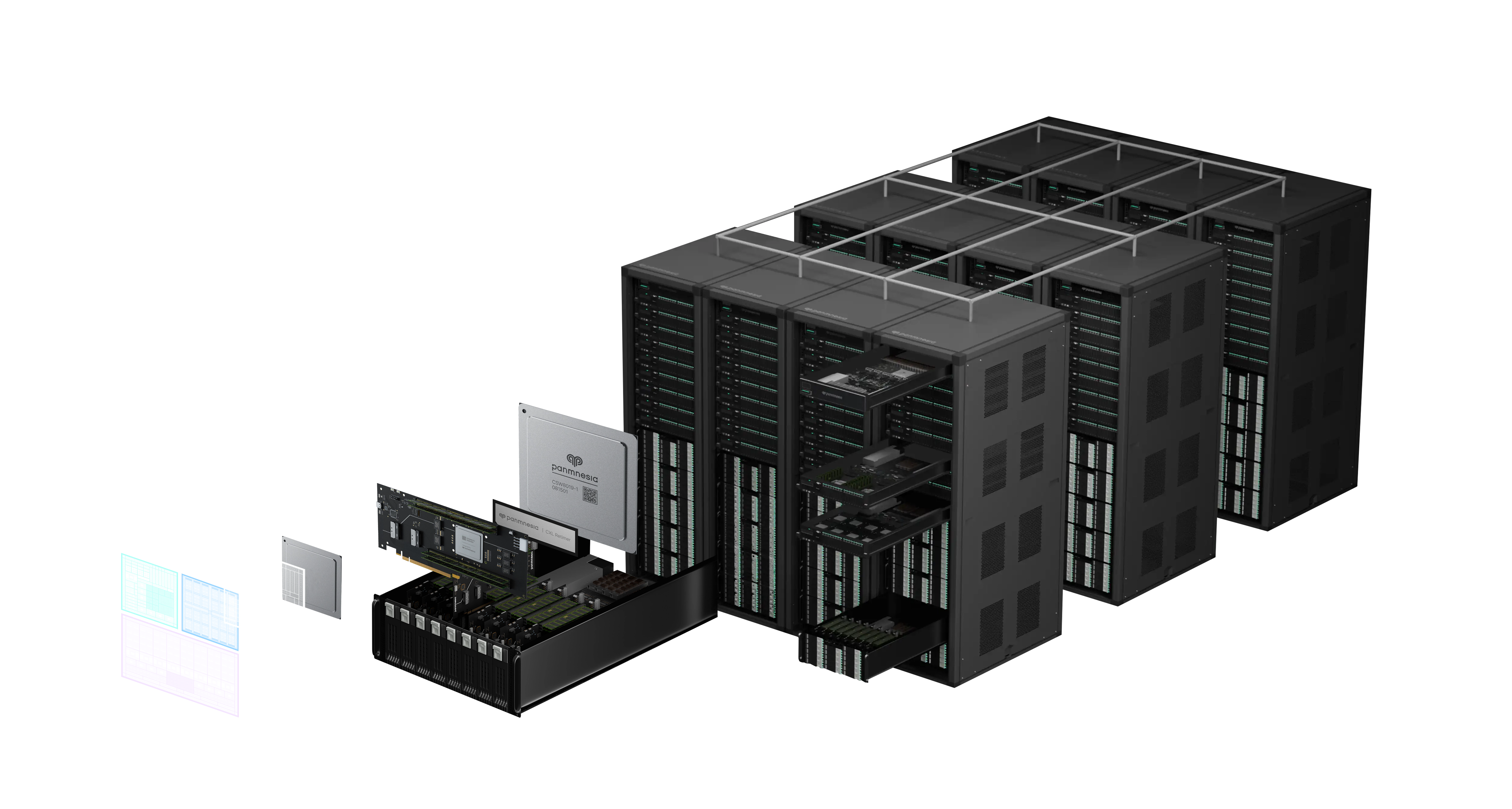

AI Training Infrastructure

Accelerate machine learning workloads with high-bandwidth memory expansion and GPU interconnects.

Ideal for large-scale AI training environments requiring massive memory capacity and ultra-low latency communication between accelerators.

Data Center Expansion

Scale your data center infrastructure with flexible CXL device connectivity and memory disaggregation.

Enables dynamic resource allocation and improves overall system efficiency in enterprise environments with growing computational demands.

HPC Cluster Computing

Connect thousands of compute nodes with ultra-low latency for high-performance computing workloads.

Ideal for scientific computing, simulation, and research applications requiring massive parallel processing and fast inter-node communication.