PCIe 6.4/CXL 3.2 Fabric Switch Silicon is Out Now

The Industry's First Fabric Switch Silicon Fully Implementing the CXL 3.2 Standard with Port-Based Routing (PBR) Support

Full Stack Link Solution Innovating the End-to-End AI Infrastructure

Panmnesia provides a link solution that empowers true composability in modern AI infrastructure

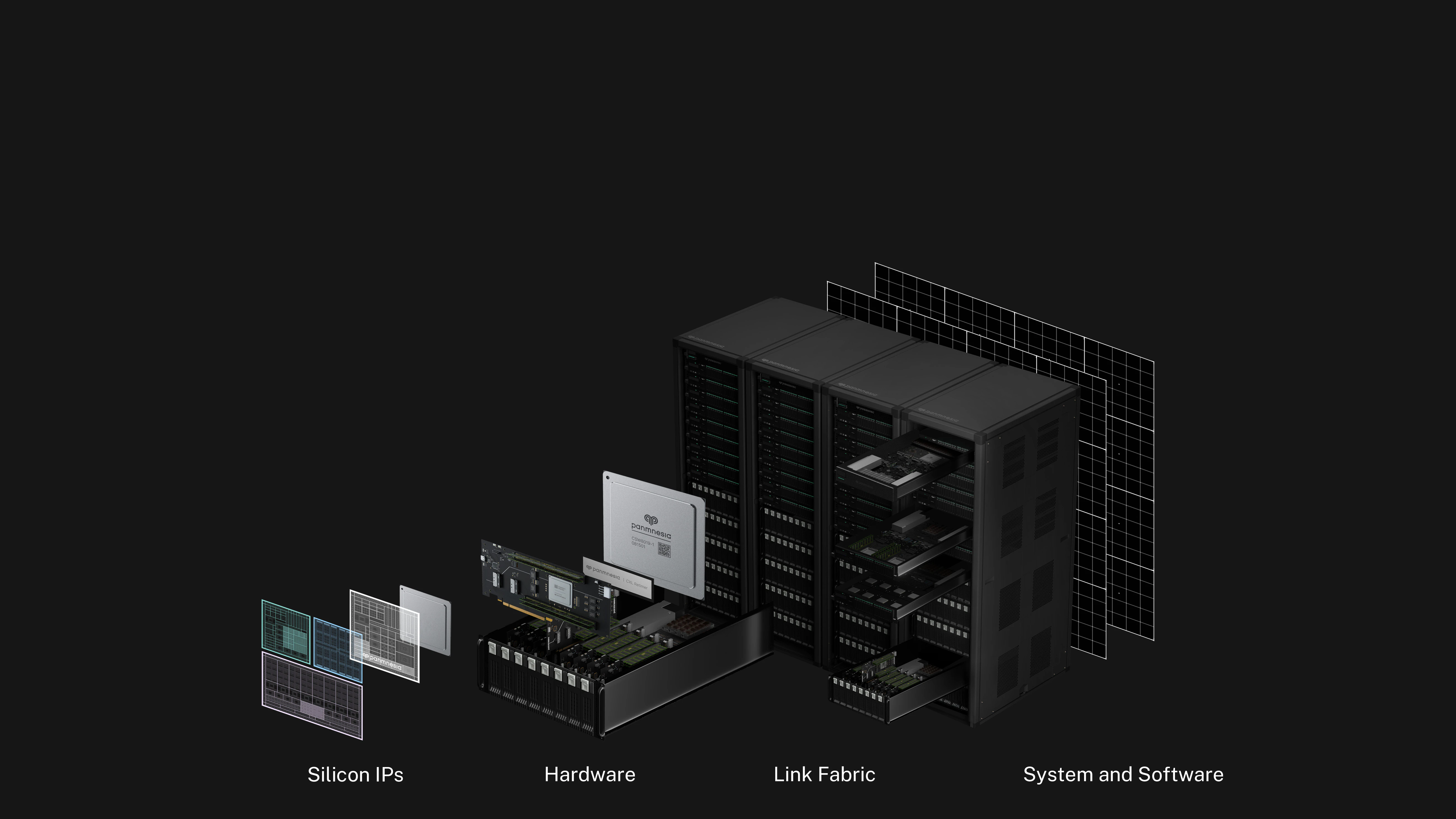

From Silicon IP and Hardware to System and Software

Panmnesia's link solution encompasses all critical technology stack for the AI infrastructure link

Each component is meticulously engineered from the ground up to support the most demanding AI workloads. Our silicon IPs incorporate advanced architectural optimizations to minimize latency and power consumption. Leveraging these IPs, our hardware establishes high-speed communication and provides the compute and memory resources composing the scalable link fabric. Our software suite completes the fabric, empowering seamless operation in data center and HPC environments.

Pioneering the New Foundation of Modern AI Infrastructure

High Scalability.

Achieve unparalleled scalability to support even the largest AI infrastructures. Built around high-fanout switches, our network topology and resource-allocation strategies enable workloads to leverage vast compute and memory resources over low-latency, high-throughput links. A robust software layer manages these connected resources with reliability and precision.

True Composability.

Unlock true composability within your AI infrastructure. Our link solution facilitates dynamic resource expansion, pooling, and sharing across disaggregated system. This maximizes the resource utilization and while minimizing the CAPEX and OPEX. It is also highly optimized to minimize link overhead and eliminate the software intervention during application execution.

Loading video...